# Multi-Level Inverter Topoloyfor Customized Winding Multi-Pole Induction Motor Drives

M. Sambasiva Rao<sup>1</sup>, Durga Prasad Killarapu<sup>2</sup>

Assistant Professor, Dept. of EEE, Loyola Institute of Technology and Management, Dhulipalla,

Andhra Pradesh, India<sup>1</sup>

M.Tech Student [P.E], Dept. of EEE, Loyola Institute of Technology and Management, Dhulipalla,

Andhra Pradesh, India<sup>2</sup>

Abstract: In this paper a five-level inverter topology is proposed for a four pole induction motor drive. This topology has developed by using the advantage of two identical voltage profile winding coils per phase in a four pole induction motor. The identical voltage profile winding coils are disconnected and each part of the winding is fed with two two-level inverters from both sides. There by four two-level inverters are used to generate five voltage levels on induction motor phase windings. All two-level inverters are fed with single DC link with the magnitude  $\frac{V_{dc}}{4}$  (where  $V_{dc}$  is the dc-bus voltage required for a conventional NPC five-level inverter). Because of the common DC link for all the two-level inverters, common mode currents will find a path through the motor phase windings due to the lack of isolated neutral. To minimize the common mode currents a Sine-Triangle Pulse Width Modulation is used in the proposed topology. There by the first dominant harmonics and triplen harmonics shifted near to the switching frequency, which will have a less impact on the motor phase currents. Since the dominant harmonics are less in the proposed topology, it gives almost sinusoidal output voltage which will improve the efficiency of the drive system. The proposed topology does not require any major design modifications of induction motor. The proposed topology is simulated in MATLAB (Simulink) with sine triangle PWM

Keywords: Five-level inverter, Induction motor drive, Sine-triangle PWM, Space-Vector PWM.

### I. INTRODUCTION

Multilevel inverter technology has been widely used for the control of medium and high voltage AC drive applications from the past few decades [1], because of its improved output voltage quality, better harmonic performance, less voltage stress on power electronic devices and etc. Many multilevel inverter configurations are presented to improve the output voltage harmonic spectrum and to reduce the circuit complexity [2]-[3] and to reduce the number of switches [4], [5]. Many Pulse Width Modulation (PWM) techniques are proposed to improve the harmonic spectrum of the voltage and currents [6]-[9].Some of the popular multilevel configurations is the Diode clamped multi-level inverter [10], flying capacitor multi-level inverter [11], [12], cascaded multi-level inverters [13]. Although they are suitable for 3-level inverters, but as the number of levels increase, the circuit and control complexity as well as switching losses increases, due to large number of devices [14]. The other alternate topology is open end winding induction motor drive fed with two-level (or multi-level) inverters [2], [6], [14]. In the open-end winding scheme, the Induction Motor windings are fed from both sides with two two-level inverters (with half the dc-link voltage when compared with conventional NPC inverter) to get a threelevel inverter topology [15]. With this concept as the number of levels increases, the inverters has to be cascaded or a conventional multi-level inverters has to be used on both the sides of the Induction Motor winding [16]. In this paper a five-level inverter topology is

proposed for the induction motor drive by using four conventional two-level inverters only, with the advantage of two identical voltage profile winding coils of four pole induction motor which will be explained in detail in the next section. The identical voltage profile winding coils are disconnected and each part of the winding is fed with two two-level inverters from both sides. There by four two-level inverters are used to generate five voltage levels on motor phase windings. All two-level inverters are fed with single DC link with the magnitude  $\frac{V_{dc}}{4}$ . The proposed topology uses sine-triangle PWM to generate the pulses for the switches of each inverter which will also minimize the common mode currents circulating in the motor phase windings because of the common DC link.

## II. DYNAMIC MODELLING OF INDUCTION MOTOR

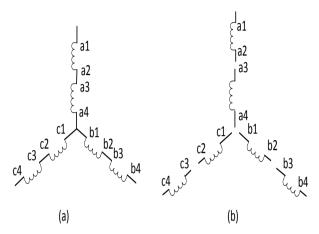

In a conventional four pole induction motor, there are two sets of identical voltage profile windings will be present in the total phase winding [17]. These two windings are connected in series as shown in fig. 1 (a). For the proposed inverter these two identical voltage profile winding coils are disconnected, and the available four terminals are taken out, like shown in the fig.1 (b). Since these two windings are separated equally, stator resistance, Stator leakage inductance and the magnetizing inductance of each identical voltage profile windings are equal to the half of the normal induction motor shown in fig.1 (a).

The voltage equitation's for the stator winding is given by

Fig. 1: Induction Motor stator winding: (a) General arrangement (b) Arrangement for the proposed inverter

The effective voltage across the stator winding is the sum of the voltages across the two individual windings.

$$V_{as} = (V_{a1} - V_{a2}) + (V_{a3}V_{a4}) \dots \dots \dots \dots (3)$$

The motor phase voltage can be achieved by substituting equations (1) and (2) in (3)

$$V_{as} = r_s * i_{as} + L_{ss} * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{bs} - \left(\frac{1}{2}\right) * L_m * i_{cs}$$

(4)

Similarly voltage equitation for the remaining phases are

$$V_{bs} = r_s * i_{bs} + L_{ss} * i_{bs} - \left(\frac{1}{2}\right) * L_m * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{cs}$$

(5)

$$V_{cs} = r_s * i_{cs} + L_{ss} * i_{cs} - \left(\frac{1}{2}\right) * L_m * i_{as} - \left(\frac{1}{2}\right) * L_m * i_{bs}$$

(6)

Where

d : direct axis,

q:quadrature axis,

- s : stator variable,

- r : rotor variable,

- $V_{qs}$ ,  $V_{ds}$ : q and d-axis stator voltages,

$V_{qr}$ ,  $V_{dr}$ : q and d-axis rotor voltages,

$r_r$ : rotor resistance,

$r_s$ : stator resistance,

L<sub>1s</sub>: stator leakage inductance,

$L_{1r}^{1s}$ : rotor leakage inductance,

$i_{qs}$ ,  $i_{ds}$ : q and d-axis stator currents,

ras, ras. q una a unis stator ca

$i_{qr}$ ,  $i_{dr}$ : q and d-axis rotor currents, p : number of poles, J : moment of inertia,  $T_e$ : electrical output torque,

$T_L$  : load torque.

From the equations (4), (5), (6) it can be observed that there is no difference between the normal induction motor shown in fig.1 (a) and the disconnected (Identical voltage profile windings) motor shown in fig.1 (b).

#### III. PROPOSED FIVE-LEVEL INVERTER TOPOLOGY

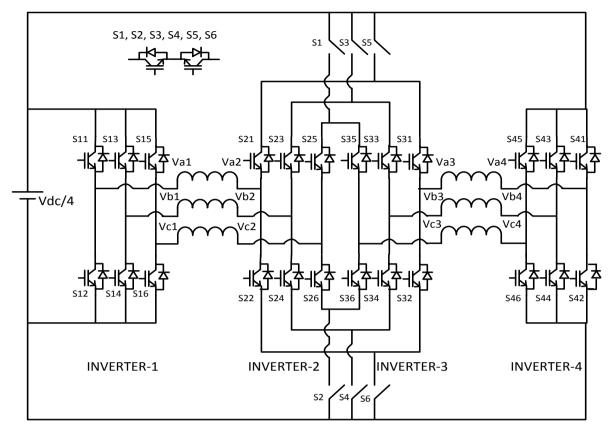

The five-level inverter topology has proposed for the four pole induction motor drive. The two identical voltage profile winding coils are disconnected, total four available terminals were taken out and fed with four two-level inverters and it is shown in fig. 2. These four two-level inverters were supplied with a single DC source having magnitude  $\frac{V_{dc}}{4}$ . In the fig.2S<sub>11</sub> to S<sub>16</sub> are the switches of the first inverter,  $S_{21}$  to  $S_{26}$  are the switches of the second inverter, S31 to S36 are the switches of the third inverter,  $S_{41}$  to  $S_{46}$  are the switches of the fourth inverter. The blocking voltage of all these switches is  $\frac{V_{dc}}{4}$ .  $(S_{11}, S_{12}), (S_{13}, S_{14}), (S_{15}, S_{16})$  are the complimentary switches of the first inverter(that is if  $S_{11}$  is on  $S_{12}$  will beoff) and it is same to remaining three inverters. The switches  $S_1$  to  $S_6$  are the auxiliary switches needed to isolate the middle two inverters (invert-2 and inverter-3 as shown in fig.2) during the voltage levels of  $-\frac{V_{dc}}{4}$ ,  $0, \frac{V_{dc}}{4}$ [2]. If the switches S<sub>1</sub> to S<sub>6</sub> are shorted, then unequal voltage distribution will happen across the motor phase windings (two identical voltage profile windings) which in turn causes unequal flux distribution and is explained clearly in [2]. The possible switching combinations available for A-phase forgenerating five voltage levels  $\left(-\frac{V_{dc}}{2}, -\frac{V_{dc}}{4}, 0, \frac{V_{dc}}{4}, \frac{V_{dc}}{2}\right)$  across motor terminals is shown in the Table-I. The proposed five-level inverter topology is compared with conventional topologies (in terms of the switching devices, capacitor banks, and isolated voltage sources), and is presented in the table-II.It can be observed that the number of main (inverter) switches required is the same for all the topologies.But the proposed topology does not require any additional clamping diodes whereas the NPC does require six diodes of rating  $3^*(\frac{V_{dc}}{4})$ , six diodes of rating  $\frac{V_{dc}}{2}$  and six diodes of rating  $\frac{V_{dc}}{4}$ . The proposed topology require one DC source having magnitude  $\frac{V_{dc}}{4}$  but H-Bridge inverter require six voltage source of magnitude  $\frac{V_{dc}}{4}$  and NPC, FC require one DC source having magnitude  $V_{dc}$ . The proposed topology does not require any capacitor banks like H-Bridge inverter but NPC requires 4 and FC requires 18 capacitor banks with voltage rating  $\frac{V_{dc}}{4}$ . However, the proposed topology requires additional six bidirectional switches with voltage rating of  $\frac{V_{dc}}{2}$ .

Fig. 2: Proposed five-level inverter

| TABLE - I POSSIBLE SWITCHING COMBINATIONS TO GENERATE FIVE VOLTAGE LEVELS |     |

|---------------------------------------------------------------------------|-----|

| TABLE - IT OSSIBLE SWITCHING COMBINATIONS TO GENERATE TIVE VOLTAGE LEVELS | · . |

| Voltage Magnitude        | <i>S</i> <sub>11</sub> | <i>S</i> <sub>21</sub> | <i>S</i> <sub>31</sub> | <i>S</i> <sub>41</sub> | $S_{A1} S_{A1'}$ | $S_{A2}S_{A2'}$ |

|--------------------------|------------------------|------------------------|------------------------|------------------------|------------------|-----------------|

| $+\frac{V_{dc}}{2}$      | ON                     | OFF                    | ON                     | OFF                    | ON               | ON              |

| $+\frac{V_{dc}}{V_{dc}}$ | ON                     | ON                     | ON                     | OFF                    | OFF              | OFF             |

| $+\frac{1}{4}$           | ON                     | OFF                    | OFF                    | OFF                    | OFF              | OFF             |

|                          | OFF                    | OFF                    | OFF                    | OFF                    | OFF              | OFF             |

|                          | ON                     | OFF                    | OFF                    | ON                     | OFF              | OFF             |

| 0                        | ON                     | ON                     | ON                     | ON                     | OFF              | OFF             |

|                          | OFF                    | ON                     | ON                     | OFF                    | OFF              | OFF             |

| $V_{dc}$                 | OFF                    | OFF                    | OFF                    | ON                     | OFF              | OFF             |

| $-\frac{1}{4}$           | OFF                    | ON                     | ON                     | ON                     | OFF              | OFF             |

| $-\frac{V_{dc}}{2}$      | OFF                    | ON                     | OFF                    | ON                     | ON               | ON              |

TABLE II COMPARISON BETWEEN THE CONVENTIONAL TOPOLOGIES WITH PROPOSED ONE

|                         |                        | NPC inverter    | FC inverter  | HB inverter               | Proposed inverter                |

|-------------------------|------------------------|-----------------|--------------|---------------------------|----------------------------------|

| switches*               |                        | 24              | 24           | 24                        | 24                               |

|                         | $3 * \frac{V_{dc}}{4}$ | 6               | 0            | 0                         | 0                                |

| Clamping<br>Diodes      | $\frac{V_{dc}}{2}$     | 6               | 0            | 0                         | 0                                |

|                         | $\frac{V_{dc}}{4}$     | 6               | 0            | 0                         | 0                                |

| Isolated vo             | oltage sources         | $1^{*}(V_{dc})$ | $1*(V_{dc})$ | $6^{*}(\frac{V_{dc}}{4})$ | $1*(\frac{V_{dc}}{4})$           |

| Capacitor Banks*        |                        | 4               | 18           | 0                         | 0                                |

| Bi-directional switches |                        | 0               | 0            | 0                         | $6\left(\frac{V_{dc}}{8}\right)$ |

#### IV. SINE TRIANGLE PULSE WIDTH MODULATION

#### a) Linear modulation region

A sine-triangle PWM for the multi-level inverters is used to generate the gating pulses for the proposed inverter topology [19]. In the Sine triangle Pulse width modulation for generating five voltage levels on motor phase winding, it requires one modulating signal and four carrier signals [19].

#### b) Over modulation (mi>1)

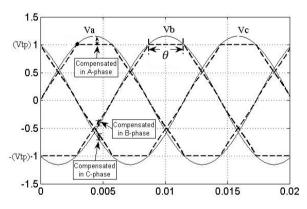

The linear modulation region can be significantly increased by adding the zero sequence component to the modulating signals in SVPWM [24]. Due to the addition of zero sequence component, the sum of instantaneous reference phase signals are not equal to zero  $(V_a+V_b+V_c \neq$ 0) which can produce lower order zero sequence currents in the motor phase windings. Therefore, SVPWM technique is not best suitable for those configurations which provide closed path for zero sequence currents (generally open end winding induction motor drives with single dc link)[19]. In this paper, a modified SPWM technique is proposed to operate the configuration in over modulation region. In this technique, whenever A-phase modulating signal is crossing peak of the upper carrier signal  $(V_{tp})$ , it is clamped to  $V_{tp}$ . The subtracted magnitude of A-phase signal (i.e.  $V_a-V_{tp}$  shown in Fig. 4) is proportionally added to B-phase and C-phase modulating signals such that the sum of three phase modulating signals equal to zero  $(V_a+V_b+V_c=0)$ . The same procedure is followed for B-phase and C-phases also.

Fig.3. Three phase modulating waves in over modulation after compensation.

#### V. RESULTS AND DISCUSSION

The propose five-level inverter is simulated with 5HP induction motor. The gating pulses, to the switches of the proposed five-level inverter, were generated with sin-triangle pulse width modulation.

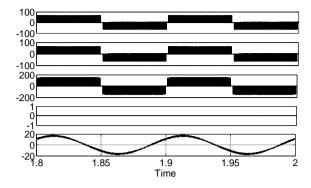

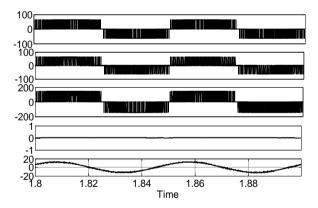

Fig. 4: Top trace is the voltage between the points A1 and A2. Second Top trace is the voltage between the points A3 and A4. Third Top trace is the effective voltage across the motor phase winding. Fourth trace is the voltage between middle two inverters (inverter-2 and inverter-3). Bottom trace is the stator current (Ia) for the modulation index=0.2 of (SPWM).

Fig. 4 shows the results for the modulation index of 0.2 (where the modulation index is equal to the ratio of peak of the modulating signal to the four times of peak of the carrier signal). From the results it is clear that the voltage across the motor phase winding is the sum of the voltage across the individual windings and the voltage profile is similar to three level operation. From fig. 4 (fourth trace from top) it is notice that, middle two inverters (inverter-2 and inverter-3) are clamped, so the switching losses in this case are less for low modulation index. Whereas, in the case of (diode clamped and Flying capacitor) multi-inverters, all the switches are needed to be switched for balancing the capacitor voltage which results in more switching losses.

The effect of common mode currents on motor phase windings is shown in Fig. 5 by using space vector PWM for the modulation Index of 0.2. In the Space Vector PWM triplen component is added to the reference voltages to get the 15% extra boost in the inverter output voltage.

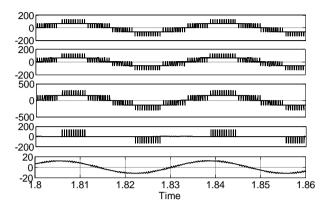

Fig. 6: Top trace is the voltage between the points A1 and A2. Second Top trace is the voltage between the points A3 and A4. Third Top trace is the effective voltage across the motor phase winding. Fourth trace is the voltage between middle two inverters. Bottom trace is thestator current (Ia) for the modulation index=0.4 of SPWM.

These common mode voltages circulate the common mode currents in motor phase windings through the common DC link. That can be clearly observed from the results shown in the fig. 5. In order to minimize this common mode currents sine triangle PWM is used for the proposed topology.

Fig. 6 shows the results for the modulation index 0.4. From the phase voltage waveform it can be observed that the inverter is operating in three level mode. From the fig. 4 and fig. 6 it can be observed that middle two inverters

are not switching, so during the switch failure of the inverter-2 and inverter-3 the proposed topology can be operated as a three-level inverter up to the modulation index of 0.5. which will increasing the reliability of the system.

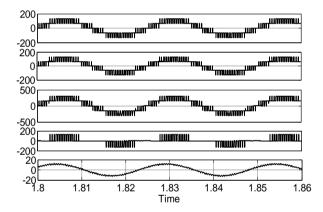

Fig. 7: Top trace is the voltage between the points A1 and A2. Second Top trace is the voltage between the points A3 and A4. Third Top trace is the effective voltage across the motor phase winding. Fourth trace is the voltage between middle two inverters. Bottom trace is thestator current (Ia) for the modulation index=0.6.

Fig. 8: Top trace is the voltage between the points A1 and A2. Second Top trace is the voltage between the points A3 and A4. Third Top trace is the effective voltage across the motor phase winding. Fourth trace is the voltage between middle two inverters. Bottom trace is the stator current (Ia) for the modulation index=0.8.

Fig. 7 shows the results for the modulation index 0.6. for this modulation index, the reference wave is passing through the all four carrier signals, thereby five voltage levels are generated across the motor terminals. From the fig.7 it can be notice that, the middle two inverters are also switched to provide the voltage levels of  $+\frac{V_{dc}}{2}$  and  $-\frac{V_{dc}}{2}$  across the motor phase windings.

Fig. 8 shows the results for the modulation index 0.8.from [1] the top fourth trace of the fig.7 and fig. 8 it is clear that middle inverters are connected to the DC link for providing the voltage levels of  $+\frac{V_{dc}}{2}$  and  $-\frac{V_{dc}}{2}$  across the [2] motor phase windings. The results for modulation index of 1.15 are shown in Fig. 9 to demonstrate the operation of the drive in over modulation region.

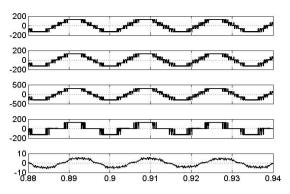

Fig. 9: Top trace is the voltage between the points A1 and A2. Second Top trace is the voltage between the points A3 and A4. Third Top trace is the effective voltage across the motor phase winding. Fourth trace is the voltage between middle two inverters. Bottom trace is the stator current (Ia) for the modulation index=1.15.

From the above results it is clear that, the proposed topology can be operated in the complete linear modulation region with sine-triangle PWM with single DC link.

#### VI. CONCLUSION

In this paper an optimized five-level inverter topology is presented for a four pole induction motor drive. This topology has developed by using the advantage of two identical voltage profile winding coils per phase in a four pole induction motor. The identical voltage profile winding coils are disconnected and each part of the winding is fed with two two-level inverters from both sides. There by four two-level inverters are required to generate five voltage levels. All two-level inverters are fed with single DC link with the magnitude  $\frac{V_{dc}}{d}$ . The proposed topology is simulated in MATLAB (Simulink) with (5HP) four pole induction motor with sine triangle PWM. From the results it can be observed that the common mode currents generated because of the single DC link were also minimized. There by the first dominant triplen harmonics and other harmonics also shifted to the switching frequency times, which will have a less impact on the motor phase currents. The proposed topology does not require any major design modifications of induction motor. An important feature of this topology is that if the middle inverter switches (inverter-2 and inverter-3) are failed, it will be operated as a three-level inverter up to the modulation index 0.5. There by the reliability of the system increases. This identical winding profile coils concept can be easily extended to 6 poles Induction motor or even more number of poles.

#### REFERENCES

- J. Rodriguez, S. Bernet, B. Wu, J. O. Pontt, and S. Kouro, "Multilevel Voltage-source-converter Topologies for Industrial Medium-voltage Drives," IEEE Transactions on Industrial Electronics., vol. 54, no. 6, pp. 2930–2945, Dec. 2007

- [2] K. Sivakumar, Anandarup Das, Rijil Ramchand, Chintan Patel, and K. Gopakumar, "A Five-Level Inverter Scheme for a Four-Pole Induction Motor Drive by Feeding the Identical Voltage-Profile Windings From Both Sides", IEEE Transactions on industrial electronics, vol. 57, No. 8, August 2010, 2776-2784.

- INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN ELECTRICAL, ELECTRONICS, INSTRUMENTATION AND CONTROL ENGINEERING Vol. 4, Issue 4, April 2016

- [3] P. P. Rajeevan, K. Sivakumar, Chintan Patel, Rijil Ramchand, and K. Gopakumar "A Seven-Level Inverter Topology for InductionMotor Drive Using Two-Level Inverters and Floating Capacitor Fed H-BridgesIEEE Transactions on power electronics, VOL. 26, NO. 6, JUNE 2011.

- [4] Javad Ebrahimi, Ebrahim Babaei, and Gevorg B. Gharehpetian, "A New Multilevel Converter Topology With Reduced Number of Power Electronic Components" IEEE Transactions on industrial electronics, VOL. 59, NO. 2, FEBRUARY 2012.

- [5] Gopal Mondal, K. Gopakumar, N. Tekwani, and Emil Levi, "A Reduced-Switch-Count Five-Level Inverter with Common-Mode Voltage Elimination for an Open-End Winding Induction Motor Drive" IEEE Transactions on Industrial Electronics, VOL. 54, NO. 4, AUGUST 2007.

- [6] Nima Yousefpoor, Seyyed Hamid Fathi, Naeem Farokhnia, and Hossein Askarian Abyaneh, "THD Minimization Applied Directly on the Line-to-Line Voltage of Multilevel Inverters" IEEE Transactions on industrial electronics, VOL. 59, NO. 1, JANUARY 2012.

- [7] Barry Venugopal Reddy, Veeramraju Timurala Somasekhar, and Yenduri Kalyan "Decoupled Space-Vector PWM Strategies for aFour-Level Asymmetrical Open-End Winding Induction Motor Drive With Waveform Symmetries" IEEE Transactions on industrial electronics, VOL. 58, NO. 11, NOVEMBER 2011

- [8] Annette von Jouanne, Shaoan Dai, and Haoran Zhang, A Multilevel Inverter Approach Providing DC-Link Balancing, Ride-Through Enhancement, and Common-Mode Voltage Elimination" IEEE Transactions on Industrial Electronics, VOL. 49, NO. 4, AUGUST 2002.

- [9] Bernardo Cougo, Guillaume Gateau, Thierry Meynard, Malgorzata Bobrowska-Rafal, and Marc Cousineau, "PD Modulation Scheme for Three-Phase Parallel Multilevel Inverters" IEEE Transactions on Industrial Electronics, VOL. 59, NO. 2, FEBRUARY 2012.

- [10] Mohan M. Renge and Hiralal M. Suryawanshi, "Five-Level Diode clamped Inverter to eliminate Common Mode Voltage and Reduced dv/dt in Medium voltage rating Induction Motor Drives, IEEE Transactions on Power Electronics, vol. 23, no.4, pp. 1598–1607 July 2008.

- [11] Mostafa Khazraei, Hossein Sepahvand, Keith A. Corzine, and Mehdi Ferdowsi, "Active Capacitor Voltage Balancing in Single-Phase Flying-Capacitor Multilevel Power Converters" IEEE Transactions on Industrial Electronics, VOL. 59, NO. 2, FEBRUARY 2012.

- [12] Xu Lie, Jon C. Clare, Patrick W. Wheeler, Lee Empringham, and Li Yongdong, "Capacitor Clamped Multilevel Matrix Converter Space Vector Modulation" IEEE Transactions on industrial electronics, VOL. 59, NO. 1, JANUARY 2012.

- [13] Fernanda Carnielutti, Humberto Pinheiro, and Cassiano Rech, "Generalized Carrier-Based Modulation Strategy for Cascaded Multilevel Converters Operating Under Fault Conditions" IEEE Transactions on Industrial Electronics, VOL. 59, NO. 2, FEBRUARY 2012.

- [14] K. Sivakumar Anandarup Das Rijil Ramchand Chintan Patel K Gopakumar, "A Hybrid Multilevel Inverter Topology for an Open-End Winding Induction-Motor Drive Using Two-Level Inverters in Series With a Capacitor-Fed H-Bridge Cell" IEEE Transactions on Industrial Electronics, Vol. 57, NO. 11, November 2010.

- [15] M. R. Baiju, K. K. Mohapatra, R. S. Kanchan and K. Gopakumar "A Dual Two-Level Inverter Scheme With Common Mode Voltage Elimination for an Induction Motor Drive" IEEE Transactions on Power Electronics, VOL. 19, NO. 3, MAY 2004.

- [16] V. T. Somasekhar, K. Gopakumar, M. R. Baiju, Krishna K. Mohapatraand L. Umanand "A Multilevel Inverter System for an Induction Motor With Open-End Windings" IEEE Transactions on Industrial Electronics, VOL. 52, NO. 3, JUNE 2005.

- [17] M. G. Say, Performance & Design A.C. Machines, 3rd ed. New Delhi,India: CBS Publishers Distributors, 1990.

- [18] Paul C. Kruase, Analysis of Electrical Machinery and Drive Systems, 2<sup>nd</sup> ed. Piscataway, NJ: IEEE press, 2002.

- [19] McGrath, B.P.; Holmes, D.G.; , "Multicarrier PWM strategies for multilevel inverters," Industrial Electronics, IEEE Transactions on , vol.49, no.4, pp. 858- 867, Aug 2002.